核心提示:優化功耗、性能和面積(PPA)一直是芯片設計中的三個重要目標。但即使是最好的設備和經驗最豐富的工程團隊也無法保證優化結果的穩

優化功耗、性能和面積(PPA)一直是芯片設計中的三個重要目標。但即使是最好的設備和經驗最豐富的工程團隊也無法保證優化結果的穩定性。

優化PPA的過程正受到越來越多因素的制約:應用、IP和其他組件的可用性不同,工程師對不同工具和方法的熟悉程度也不盡相同。例如,同樣的設計目標既可以用更大的處理器實現更高性能,也可以用更小、更專業的處理元件更緊密的結合軟件來實現。因此,即使在相同領域和相同的功率設計目標下,也會有許多不同的方法可以實現相同的目標。并且方案優劣的評價標準也是因領域和供應商的具體需求而異的。 另外,由于對芯片安全性的需求不斷增加,優化過程變得愈加復雜。根據設備使用場景的重要性,其安全需求也各不相同。安全級別的高低會影響芯片功率和性能的設計,進一步影響IC制造成本、上市時間、交貨時間和供應商的競爭力。

另外,由于對芯片安全性的需求不斷增加,優化過程變得愈加復雜。根據設備使用場景的重要性,其安全需求也各不相同。安全級別的高低會影響芯片功率和性能的設計,進一步影響IC制造成本、上市時間、交貨時間和供應商的競爭力。

為了縷清這些因素,EDA供應商開始尋求人工智能和機器學習技術的幫助。芯片供應商們正致力于將各種AI功能集成到工具流中。根據麻省理工學院和德克薩斯大學奧斯汀分校的研究人員的論文,迄今為止該領域研究成果喜人。研究人員表示,使用了深度強化學習算法的設備在某些任務上的表現已經超過了人類。

在六個小時的實驗中,研究人員通過對比使用強化學習的圖卷積神經網絡方法、傳統的黑盒優化方法(貝葉斯優化、進化算法)、隨機搜索方法、具有五年經驗的設計師這四者的成果得到結論:帶有遷移學習的強化學習方法可以取得更好的效果。換言之,基于人工智能的工具可以使晶體管設計更加高效。

如今,包括谷歌、英偉達、新思科技、Cadence、三星和西門子在內的許多公司都已經有在芯片設計中使用人工智能的計劃,其中部分公司甚至已經在生產中進行這種嘗試。

人工智能如何改變芯片設計格局?

直到今天,人們在設計芯片的過程中仍然在使用各種設計工具進行電路、邏輯門、布線、布局的仿真和驗證。這么做是為了最大限度的減少可能的錯誤并且節約時間和成本,但這個過程相當乏味且耗時。

AI比人類更懂芯片設計?

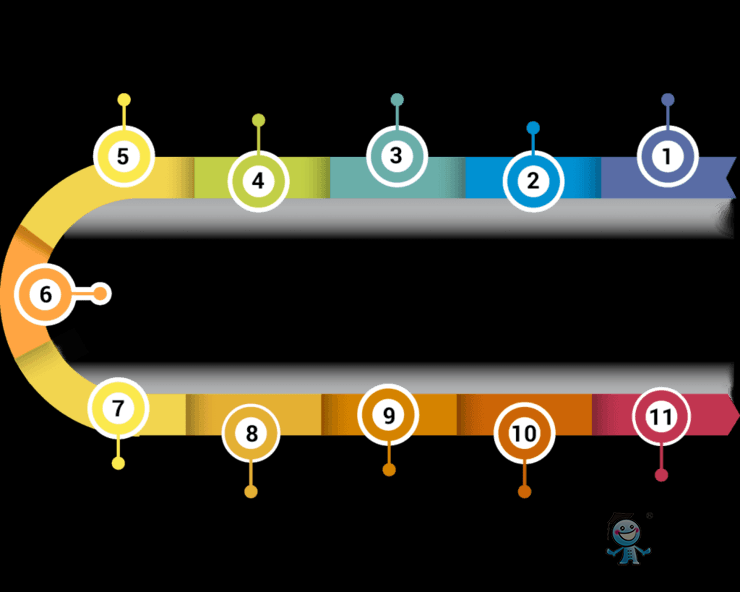

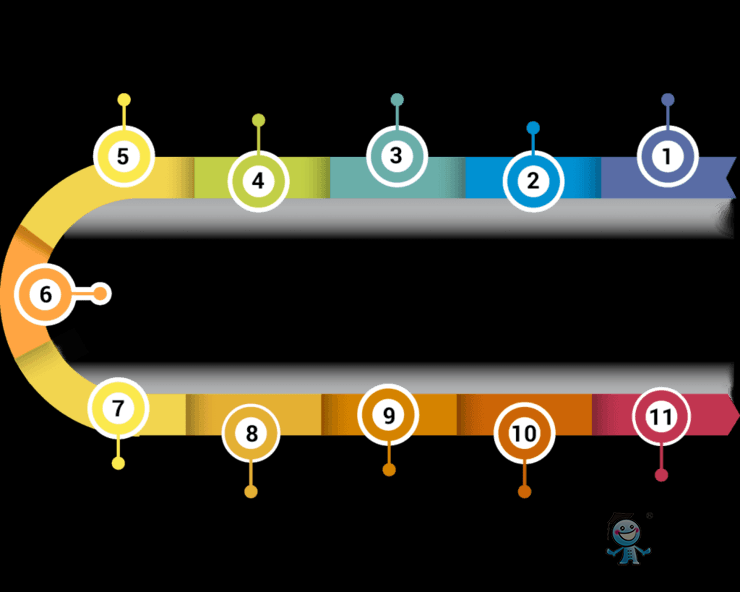

圖 1:半導體設計流程中的各個步驟。 資料來源:eInfochips

設計芯片的流程有很多步驟:一般從確定芯片的規格和架構開始,然后遵循上面流程圖中的各個步驟。在設計完成后,設計文件(GDS II)將會被發送給工廠。

當摩爾定律有效時,這個流程只需要根據實際情況進行微調即可。但隨著制程紅利正在消失,FinFET時代到來。由于先進制程研發成本的增高,芯片制造商們不得不開始尋找新的方法來實現PPA的優化。這種新變化顯著增加了芯片設計流程的復雜程度,并使得按期交付芯片愈加困難。

“設計一個28nm芯片的平均成本僅為4000萬美元,”IBS首席執行官Handel Jones說,“但現在設計一個7nm芯片的成本是2.17億美元,設計一個5nm芯片的成本則是4.16億美元,設計一個3nm芯片的成本甚至達到了5.9億美元。”

隨著芯片的迭代,晶體管數量已經從幾千個增加到了數十億個。這使得芯片上晶體管排布設計的異構性越來越高,并且它們通常都會采用某種先進封裝工藝。與之前只需要考慮如何將更多的晶體管排列在同一空間不同,現在芯片設計中還需要考慮到功率密度、熱預算需求、各種類型的機械和電氣應力、鄰近效應以及工作環境等復雜因素。這使得設計過程耗時大大增加,同時也堆高了設計成本。更糟糕的是,芯片制造商間的持續競爭迫使他們必須在更短時間內實現芯片的迭代,否則就會在競爭中處于劣勢。這導致了芯片制造商沒有試錯機會:一次設計失誤就代表著巨額損失。

優化PPA的過程正受到越來越多因素的制約:應用、IP和其他組件的可用性不同,工程師對不同工具和方法的熟悉程度也不盡相同。例如,同樣的設計目標既可以用更大的處理器實現更高性能,也可以用更小、更專業的處理元件更緊密的結合軟件來實現。因此,即使在相同領域和相同的功率設計目標下,也會有許多不同的方法可以實現相同的目標。并且方案優劣的評價標準也是因領域和供應商的具體需求而異的。

為了縷清這些因素,EDA供應商開始尋求人工智能和機器學習技術的幫助。芯片供應商們正致力于將各種AI功能集成到工具流中。根據麻省理工學院和德克薩斯大學奧斯汀分校的研究人員的論文,迄今為止該領域研究成果喜人。研究人員表示,使用了深度強化學習算法的設備在某些任務上的表現已經超過了人類。

在六個小時的實驗中,研究人員通過對比使用強化學習的圖卷積神經網絡方法、傳統的黑盒優化方法(貝葉斯優化、進化算法)、隨機搜索方法、具有五年經驗的設計師這四者的成果得到結論:帶有遷移學習的強化學習方法可以取得更好的效果。換言之,基于人工智能的工具可以使晶體管設計更加高效。

如今,包括谷歌、英偉達、新思科技、Cadence、三星和西門子在內的許多公司都已經有在芯片設計中使用人工智能的計劃,其中部分公司甚至已經在生產中進行這種嘗試。

人工智能如何改變芯片設計格局?

直到今天,人們在設計芯片的過程中仍然在使用各種設計工具進行電路、邏輯門、布線、布局的仿真和驗證。這么做是為了最大限度的減少可能的錯誤并且節約時間和成本,但這個過程相當乏味且耗時。

AI比人類更懂芯片設計?

圖 1:半導體設計流程中的各個步驟。 資料來源:eInfochips

設計芯片的流程有很多步驟:一般從確定芯片的規格和架構開始,然后遵循上面流程圖中的各個步驟。在設計完成后,設計文件(GDS II)將會被發送給工廠。

當摩爾定律有效時,這個流程只需要根據實際情況進行微調即可。但隨著制程紅利正在消失,FinFET時代到來。由于先進制程研發成本的增高,芯片制造商們不得不開始尋找新的方法來實現PPA的優化。這種新變化顯著增加了芯片設計流程的復雜程度,并使得按期交付芯片愈加困難。

“設計一個28nm芯片的平均成本僅為4000萬美元,”IBS首席執行官Handel Jones說,“但現在設計一個7nm芯片的成本是2.17億美元,設計一個5nm芯片的成本則是4.16億美元,設計一個3nm芯片的成本甚至達到了5.9億美元。”

隨著芯片的迭代,晶體管數量已經從幾千個增加到了數十億個。這使得芯片上晶體管排布設計的異構性越來越高,并且它們通常都會采用某種先進封裝工藝。與之前只需要考慮如何將更多的晶體管排列在同一空間不同,現在芯片設計中還需要考慮到功率密度、熱預算需求、各種類型的機械和電氣應力、鄰近效應以及工作環境等復雜因素。這使得設計過程耗時大大增加,同時也堆高了設計成本。更糟糕的是,芯片制造商間的持續競爭迫使他們必須在更短時間內實現芯片的迭代,否則就會在競爭中處于劣勢。這導致了芯片制造商沒有試錯機會:一次設計失誤就代表著巨額損失。

在線客服

在線客服

企業微信

企業微信